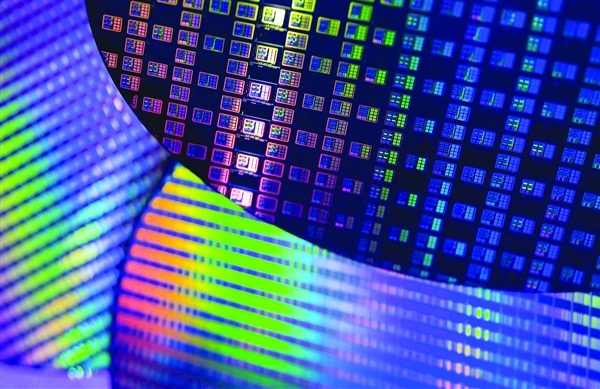

臺積電3nm艱難量產 真正有產品放量還要到2023年

2022年本來該是半導體工藝轉向3nm量產的一年,然而今年臺積電低調了許多,三星搶在6月份就宣布率先3nm工藝,搶走了名義上的3nm首發,臺積電早前提到的9月份量產早已無效,官方承諾的是年底。

距離2022年還剩下最后幾天了,臺積電總算兌現了承諾,日前公司發布邀請函,下周將在南科舉辦量產暨擴廠典禮,屆時會正式量產3nm工藝。

這個時間點宣布量產,2022年的3nm產量可以忽略不記,只是讓臺積電兌現今年量產3nm的承諾,真正有產品放量還要到2023年。

臺積電之前公布了至少5種3nm工藝,現在還不好確定即將量產的是N3還是N3E,前者此前有爆料稱已經被放棄,因為成本太高,蘋果也不用了,導致沒有客戶,量產沒有意義。

根據臺積電說法,對比N5工藝,N3功耗可降低約25-30%,性能可提升10-15%,晶體管密度提升約70%。

但是N3工藝實際的表現不一定有這么好,前不久在IEDM 2022大會上,臺積電論文種公布了3nm下SRAM的真實密度,表現讓人很擔心。

3工藝的SRAM單元的面積為0.0199平方微米,相比于N5工藝的0.021平方微米只縮小了區區5%!

更糟糕的是,所謂的第二代3nm工藝N3E,SRAM單元面積為0.021平方微米,跟N5工藝毫無差別。

臺積電這樣擠牙膏的提升,讓Intel有了追趕回來的機會,雖然3nm的SRAM密度還是要比Intel的10nm ESF(現在的Intel 7)高不少,但跟Intel的7nm EUV工藝(現在的Intel 4)相差無幾。

臺積電在下一代的2nm工藝上晶體管密度提升更少,官方數據也不過10%-20%,解釋很容易就被Intel的20A、18A工藝超越了。

來源:快科技

IT時代網(關注微信公眾號ITtime2000,定時推送,互動有福利驚喜)所有原創文章版權所有,未經授權,轉載必究。

創客100創投基金成立于2015年,直通硅谷,專注于TMT領域早期項目投資。LP均來自政府、互聯網IT、傳媒知名企業和個人。創客100創投基金對IT、通信、互聯網、IP等有著自己獨特眼光和豐富的資源。決策快、投資快是創客100基金最顯著的特點。

熱門文章

精彩評論

小何華為現在牛的不只是設備商了,,華為的手機現在也是全球銷量不錯,國內也算是老大了,之前用小米,,現在都改華為了。。產品確實不錯。

小何華為現在牛的不只是設備商了,,華為的手機現在也是全球銷量不錯,國內也算是老大了,之前用小米,,現在都改華為了。。產品確實不錯。 小何三星手機在中國還有市場嗎?看看現在滿大街的vivo和oppo ,,華為,,小米線下店,,就是知道三星的市場基本沒有了。。

小何三星手機在中國還有市場嗎?看看現在滿大街的vivo和oppo ,,華為,,小米線下店,,就是知道三星的市場基本沒有了。。 小何滴滴打車現在也沒有之前那么火了,,補貼也少了。。

小何滴滴打車現在也沒有之前那么火了,,補貼也少了。。 小何今日頭條要把騰訊的地方各頻道給霸占了。。

小何今日頭條要把騰訊的地方各頻道給霸占了。。